新材料・機能集積で切り拓く超低消費電力CMOS半導体デバイス

半導体デバイス研究の最先端で、今世界中でホットに進められている研究にすぐに飛び込んで見たい方、これまで学んできた物性理論や半導体の知識が実際どのように役立つのか実感して見たい方など、意欲的な皆さんの参加を期待します

研究分野1

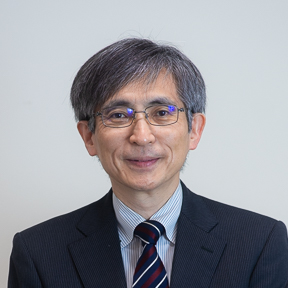

強誘電体ゲート絶縁膜MOSFET(FeFET)とFeRAM

分極反転を伴う強誘電体をゲート絶縁膜としたMOSFET(FeFET)や金属とのサンドイッチ構造(MFM構造)をメモリセルとするFeRAMは、将来の極低消費電力メモリやロジック用素子として期待されている。特に近年発見されたHfZrO2やZrO2などの強誘電体・反強誘電体を用いたデバイスは、現在のSi CMOSテクノロジーとの親和性が極めて高く、大きな関心を集めている。しかしながら、その素子動作や材料物性は不明な点が多く、更なる高性能化・高信頼性化への要求も高い。当研究室では、原子層堆積(ALD)法によって堆積したこれら強誘電体薄膜の物性やFeFETの素子動作原理の明確化を通じて、優れた素子特性を実現する研究を進めている。

研究分野2

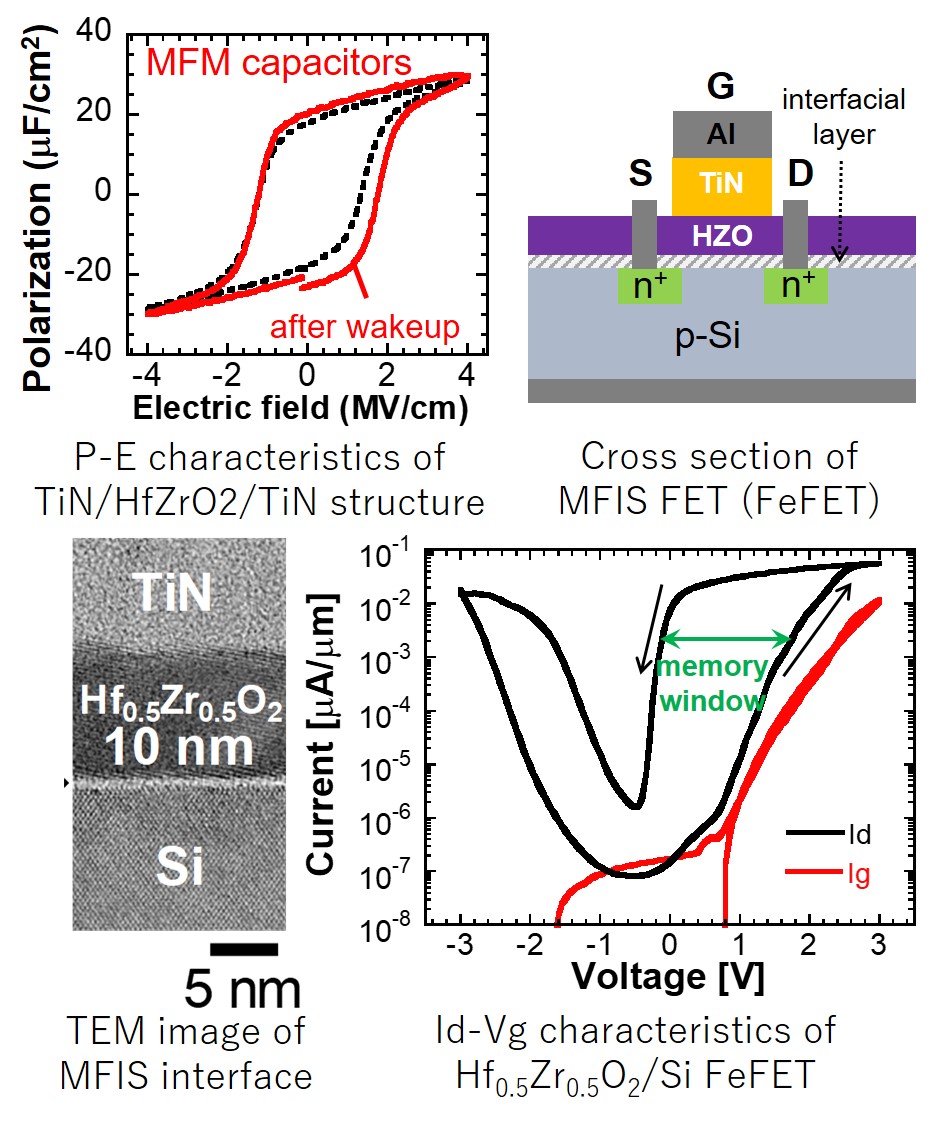

強誘電体デバイスを用いたリザバーコンピューティング

計算負荷の軽いAI計算手法として、リザバーコンピューティングが近年注目を集めている。当研究室では、メモリ・イン・ロジック機能や非線形アナログ計算機能をもつ強誘電体ゲートMOSFET(FeFET)やMFMキャパシタが、リザバーコンピューティングを物理実装できるハードウェアとして有望であることを提案し、そのリザバーコンピューティング動作を世界で初めて実証している。強誘電体デバイスを用いたこのリザバーを用いて、極低消費電力で推論・学習を行うことができる新しいAIハードウェアをSiプラットフォーム上に実現する研究を行っている。

研究分野3

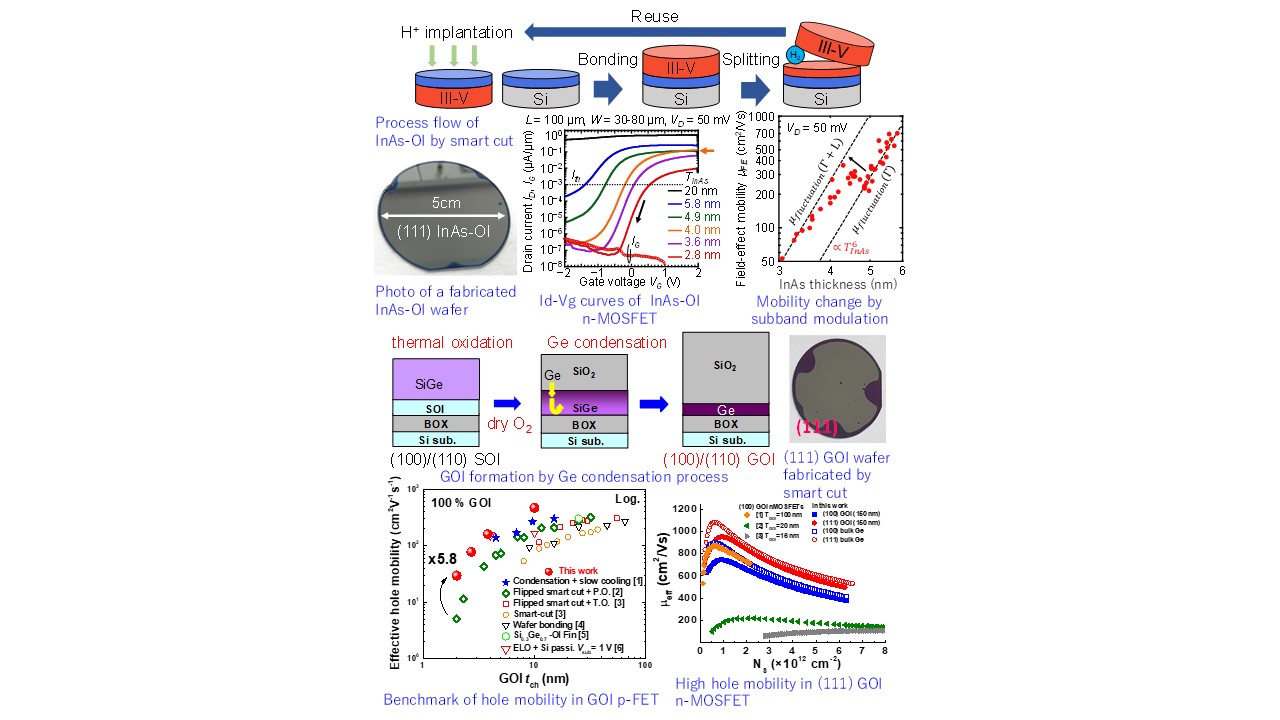

3次元集積CMOSのための極薄膜Ge-On-Insulator/III-V-On-Insulator MOSFET

将来のロジックLSIの本命デバイスして、トランジスタを縦型に積層した3次元集積CMOSが期待されている。このような積層型MOSFETを実現する上では、低温で素子が作製できかつ高い移動度や注入速度が期待できるIII-V化合物半導体やGeなどのチャネルが有望である。当研究室では、3次元集積CMOSを目指して、Si基板上に極薄のGe-On-Insulator(GOI)やIII-V-On-Insulator (III-V-OI)構造を実現する技術やこの構造をチャネルに用いたMOSFETの実証と高性能化、その電気特性を決定しているデバイス物理の研究を進めている。smart cut法などを用いたオリジナリティの高い基板形成技術、高品質MOS界面制御技術などにより、世界最高レベルのMOSFET性能を実証すると共に、キャリア輸送特性の明確化を進め、世界的にも高い関心を集めている。